# Lecture Notes in Computer Science

5335

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

## **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Alfred Kobsa

University of California, Irvine, CA, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

José Nelson Amaral (Ed.)

# Languages and Compilers for Parallel Computing

21st International Workshop, LCPC 2008 Edmonton, Canada, July 31 – August 2, 2008 Revised Selected Papers

#### Volume Editor

José Nelson Amaral University of Alberta Department of Computing Science Edmonton, AB, T6G-2E8, Canada E-mail: amaral@cs.ualberta.ca

Library of Congress Control Number: 2008940024

CR Subject Classification (1998): D.1.3, C.2.4, D.4.2, H.3.4, D.2

LNCS Sublibrary: SL 1 – Theoretical Computer Science and General Issues

ISSN 0302-9743

ISBN-10 3-540-89739-9 Springer Berlin Heidelberg New York ISBN-13 978-3-540-89739-2 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2008 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 12567744 06/3180 5 4 3 2 1 0

# Preface

In 2008 the Workshop on Languages and Compilers for Parallel Computing left the USA to celebrate its 21st anninversary in Edmonton, Alberta, Canada. Following its long-established tradition, the workshop focused on topics at the frontier of research and development in languages, optimizing compilers, applications, and programming models for high-performance computing. While LCPC continues to focus on parallel computing, the 2008 edition included the presentation of papers on program analysis that are precursors of high performance in parallel environments.

LCPC 2008 received 35 paper submissions. Each paper received at least three independent reviews, and then the papers and the referee comments were discussed during a Program Committee meeting. The PC decided to accept 18 papers as regular papers and 6 papers as short papers. The short papers appear at the end of this volume.

The LCPC 2008 program was fortunate to include two keynote talks. Keshav Pingali's talk titled "Amorphous Data Parallelism in Irregular Programs" argued that irregular programs have data parallelism in the iterative processing of worklists. Pingali described the Galois system developed at The University of Texas at Austin to exploit this kind of amorphous data parallelism.

The second keynote talk, "Generic Parallel Algorithms in Threading Building Bocks (TBB)," presented by Arch Robison from Intel Corporation addressed very practical aspects of using TBB, a production C++ library, for generic parallel programming and contrasted TBB with the Standard Template Library (STL).

LCPC continues to be a strong workshop thanks to the support that it enjoys from both the programming language and optimizing compiler communities and from the various segments of the high-performance computing community. The continued strength of LCPC is also in no small part due to the passionate commitment of David Padua and the Steering Committee as well as due to the time commitment of Program Committee members, anonymous reviewers, and contributing authors. We are grateful for the financial support provided by iCore. The organization of LCPC by the Department of Computing Science at the University of Alberta in Edmonton counted on outstanding volunteers including Fran Moore, Sheryl Maiko, and Sunrose Ko.

September 2008

José Nelson Amaral

# Organization

LCPC 2008 was organized by the Department of Computing Science, University of Alberta, Edmonton, Alberta, Canada

### Executive Committee

# General and Program Chair

José Nelson Amaral University of Alberta

# Steering Committee

Rudolf Eigenmann Purdue University

Alex Nicolau University of California at Irvine

David Padua University of Illinois at Urbana Champaign

Lawrence Reuchwerger Texas A&M University

# **Program Committee**

Vikram Adve University of Illinois at Urbana Champaign

Gheorghe Almási IBM T.J. Watson Research Center

José Nelson Amaral University of Alberta

Eduard Ayguadé Universitat Politécnica de Catalunya

Gerald Baumgartner Louisiana State University

Călin Caşcaval IBM T.J. Watson Research Center

John Cavazos University of Delaware

María Garzarán University of Illinois at Urbana-Champaign

Xiaoming Li University of Delaware

Lori Pollock University of Delaware

J. Ramanujam Louisiana State University

P. Sadayappan Ohio State University

Peng Wu IBM T.J. Watson Research Center

# Sponsoring Institutions

Department of Computing Science, University of Alberta, Edmonton, AB, Canada

Informatics Circle of Research Excellence (iCORE), Alberta, Canada

# **Table of Contents**

| Sain-Zee Ueng, Melvin Lathara, Sara S. Baghsorkhi, and Wen-mei W. Hwu                                                                  | 1   |

|----------------------------------------------------------------------------------------------------------------------------------------|-----|

| MCUDA: An Efficient Implementation of CUDA Kernels for Multi-core CPUs                                                                 | 16  |

| Automatic Pre-Fetch and Modulo Scheduling Transformations for the Cell BE Architecture                                                 | 31  |

| Efficient Set Sharing Using ZBDDs                                                                                                      | 47  |

| Register Bank Assignment for Spatially Partitioned Processors  Behnam Robatmili, Katherine Coons, Doug Burger, and Kathryn S. McKinley | 64  |

| Smashing: Folding Space to Tile through Time                                                                                           | 80  |

| Identification of Heap-Carried Data Dependence Via Explicit Store Heap Models                                                          | 94  |

| On the Scalability of an Automatically Parallelized Irregular Application                                                              | 109 |

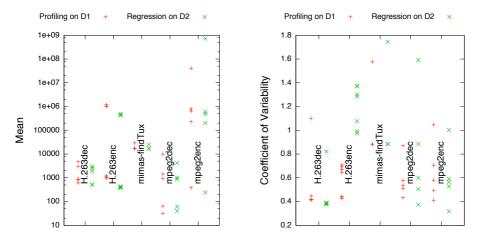

| Statistically Analyzing Execution Variance for Soft Real-Time Applications                                                             | 124 |

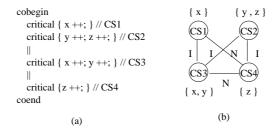

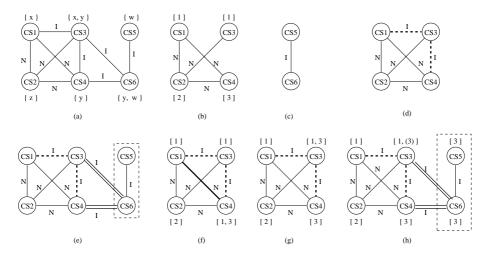

| Minimum Lock Assignment: A Method for Exploiting Concurrency among Critical Sections                                                   | 141 |

| (TLS)                                                                                                                                  | 156 |

|----------------------------------------------------------------------------------------------------------------------------------------|-----|

| Cosmin E. Oancea and Alan Mycroft                                                                                                      |     |

| Thread Safety through Partitions and Effect Agreements                                                                                 | 172 |

| P-Ray: A Software Suite for Multi-core Architecture                                                                                    |     |

| Characterization                                                                                                                       | 187 |

| Scalable Implementation of Efficient Locality Approximation $Xipeng\ Shen\ and\ Jonathan\ Shaw$                                        | 200 |

| P-OPT: Program-Directed Optimal Cache Management                                                                                       | 217 |

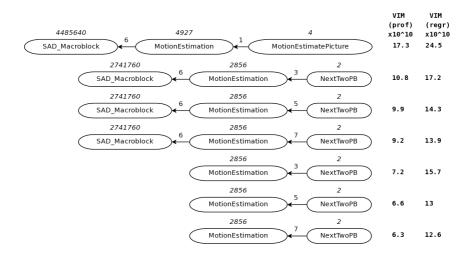

| Compiler-Driven Dependence Profiling to Guide Program                                                                                  |     |

| Parallelization                                                                                                                        | 232 |

| gluepy: A Simple Distributed Python Programming Framework for Complex Grid Environments                                                | 249 |

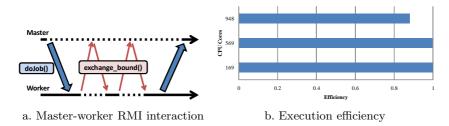

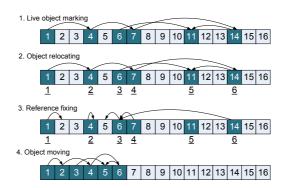

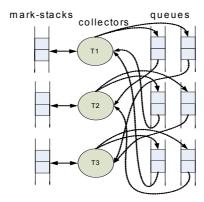

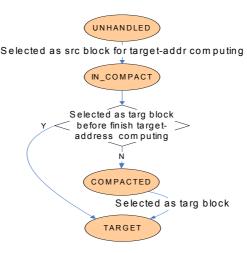

| A Fully Parallel LISP2 Compactor with Preservation of the Sliding Properties                                                           | 264 |

| A Case Study in Tightly Coupled Multi-paradigm Parallel                                                                                |     |

| Programming                                                                                                                            | 279 |

| ASYNC Loop Constructs for Relaxed Synchronization                                                                                      | 292 |

| Design for Interoperability in STAPL: pMatrices and Linear Algebra                                                                     |     |

| Algorithms  Antal A. Buss, Timmie G. Smith, Gabriel Tanase,  Nathan L. Thomas, Mauro Bianco, Nancy M. Amato, and  Lawrence Rauchwerger | 304 |

| Implementation of Sensitivity Analysis for Automatic Parallelization Silvius Rus. Maikel Penninas, and Lawrence Rauchwerger            | 316 |

| Just-In-Time Locality and Percolation for Optimizing Irregular Applications on a Manycore Architecture | 331 |

|--------------------------------------------------------------------------------------------------------|-----|

| Exploring the Optimization Space of Dense Linear Algebra Kernels Qing Yi and Apan Qasem                | 343 |

| Author Index                                                                                           | 357 |

Table of Contents

IX

# CUDA-Lite: Reducing GPU Programming Complexity

Sain-Zee Ueng, Melvin Lathara, Sara S. Baghsorkhi, and Wen-mei W. Hwu

Center for Reliable and High-Performance Computing Department of Electrical and Computer Engineering University of Illinois at Urbana-Champaign {ueng,mlathara,bsadeghi,hwu}@crhc.uiuc.edu

Abstract. The computer industry has transitioned into multi-core and many-core parallel systems. The CUDA programming environment from NVIDIA is an attempt to make programming many-core GPUs more accessible to programmers. However, there are still many burdens placed upon the programmer to maximize performance when using CUDA. One such burden is dealing with the complex memory hierarchy. Efficient and correct usage of the various memories is essential, making a difference of 2-17x in performance. Currently, the task of determining the appropriate memory to use and the coding of data transfer between memories is still left to the programmer. We believe that this task can be better performed by automated tools. We present CUDA-lite, an enhancement to CUDA, as one such tool. We leverage programmer knowledge via annotations to perform transformations and show preliminary results that indicate auto-generated code can have performance comparable to hand coding.

# 1 Introduction

In 2007, NVIDIA introduced the Compute Unified Device Architecture (CUDA) [9], an extended ANSI C programming model. Under CUDA, Graphics Processing Units (GPUs) consist of many processor cores, each of which can directly address into a global memory. This allows for a much more flexible programming model than previous GPGPU programming models [11], and allows developers to implement a wider variety of data-parallel kernels. As a result, CUDA has rapidly gained acceptance in application domains where GPUs are used to execute compute intensive, data-parallel application kernels.

While GPUs have been designed with higher memory bandwidth than CPUs, the even higher compute throughput of GPUs can easily saturate their available memory bandwidth. For example, the NVIDIA GeForce 8800 GTX comes with 86.4 GB/s memory bandwidth, approximately ten times that of Intel CPUs on a Front Side Bus. However, since the GeForce 8800 has a peak performance of 384 GFLOPS and each floating point operation operates on up to 12 bytes of source data, the available memory bandwidth cannot sustain even a small fraction of the peak performance if all of the source data are accessed from global memory.

Consequently, CUDA and its underlying GPUs offer multiple memory types with different bandwidth, latency, and access restrictions to allow programmers

to conserve memory bandwidth while increasing the overall performance of their applications. Currently, CUDA programmers are responsible for explicitly allocating space and managing data movement among the different memories to conserve memory bandwidth. Furthermore, additional hardware mechanisms at the memory interface can enhance the main memory access efficiency if the access patterns follow memory coalescing rules. Currently, CUDA programmers shoulder the responsibility of massaging the code to produce the desirable access patterns. Experiences show that such responsibility presents a major burden on the programmer. CUDA-lite is designed to relieve such burden. Furthermore, CUDA code that is explicitly optimized for one GPU's memory hierarchy design may not easily port to the next generation or other types of data-parallel execution vehicles.

This paper presents CUDA-lite, an experimental enhancement to CUDA that allows programmers to deal only with global memory, the main memory of a GPU, with transformations to leverage the complex memory hierarchy. For increased efficiency, the programmers provide annotations describing certain properties of the data structures and code regions designated for GPU execution. The CUDA-lite tools analyze the code along with these annotations and determine if the memory bandwidth can be conserved and latency can be reduced by utilizing any special memory types and/or by massaging memory access patterns. Upon detection of an opportunity, CUDA-lite performs the transformations and code insertions needed. CUDA-lite is designed as a source-to-source translator. The output is CUDA code with explicit memory-type declarations and data transfers for a particular GPU. We envision CUDA-lite to eventually target multiple types and generations of data-parallel execution vehicles. If maximum performance is desired, the programmer can still choose to program certain kernels at the CUDA level.

In this paper we present CUDA-lite in detail. We cover the memories and techniques that are leveraged by the tool to conserve memory bandwidth and reduce memory latency. We describe how CUDA-lite identifies the opportunities and the hand transformations that it replaces. We have developed plug-ins for the Phoenix compiler [7] from Microsoft to perform all of the transformations as a source-to-source compiler, and evaluated our results by passing the resulting source code through NVIDIA's tool chain. We show that the performance of code generated by CUDA-lite matches or is comparable to hand generated code.

# 2 CUDA Programming Model

The CUDA programming model is ANSI C extended with keywords and constructs. The GPU is treated as a coprocessor that executes data-parallel kernel functions. The user supplies a single source program encompassing both host (CPU) and kernel (GPU) code. These are separated and compiled by NVIDIA's compiler, *nvcc*. The host starts the kernel code with a function call. The complete description of the programming model can be found in [8,9,10].

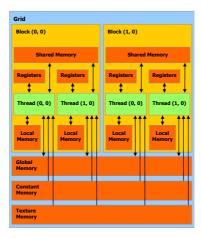

Fig. 1. CUDA Programming Model and Memory Hierarchy

Figure 1 depicts the programming model and memory hierarchy of CUDA. Threads are organized into a three-level hierarchy, and are executed on the streaming multiprocessors (SMs) on the GPU. At the highest level, each kernel creates a single grid, which consists of many thread blocks (TBs) arranged in two dimensions. The maximum number of threads per TB is 512, arranged in a three dimensional manner. Each TB is assigned to a single SM for its execution. Each SM can handle up to eight TBs at a time. Threads in the same TB can share data through the on-chip shared memory and can perform barrier synchronization by invoking the <u>syncthreads</u> primitive. Synchronization across TBs can only be safely accomplished by terminating the kernel.

One of the major bottleneck to achieving performance while using CUDA is the memory bandwidth and latency. The GPU provides several different memories with different behaviors and performance that can be leveraged to improve memory performance. However, the programmer must explicitly and correctly utilize these different memories in the source code in order to gain the benefit. In the rest of this section we will examine *shared memory* and desirable memory access patterns to *global memory* that improve memory performance, and show the work required of programmers. Work that CUDA-lite intends to automate.

We focus on memory coalescing for global memory and shared memory in this work since these are the only writable memories in CUDA. We leave the read-only memories, constant and texture, for future work.

# 2.1 Global Memory

CUDA exposes a general-purpose, random access, readable and writable off-chip global memory visible to all threads. It is the slowest of the available memory spaces, requiring hundreds of cycles, and is not cached. However, its resemblance to a CPU's memory in its generality and size are also what allows more

```

#define ASIZE 3000

int main ()

#define TPB 256

int num blocks;

_global__ void

int size = sizeof (float) * ASIZE * ASIZE;

5 kernel (float *a, float *b)

/* Allocate a_host and b_host,

int thi = threadIdx.x;

* and initialize a host with values */

int bki = blockIdx.x;

float t = (float) thi + bki;

/* Allocate a_device and b_device */

10

cudaMalloc ((void **) &a_device, size);

cudaMalloc ((void **) &b_device, size);

if (bki * TPB + thi >= ASIZE)

return;

/* Copy values from host to device */

cudaMemcpy (a_device, a_host, size,

15

for (i = 0; i < ASIZE; i++)

cudaMemcpyHostToDevice);

b[(bki*TPB+thi)*ASIZE + i] =

num_blocks = ASIZE % TPB == 0 ?

a[(bki*TPB+thi)*ASIZE + i] * t;

ASIZE / TPB : (ASIZE / TPB) + 1;

20 }

/* Number of thread blocks in the grid */

dim3 gridDim (num blocks);

/* Number of threads per thread block */

dim3 blockDim (TPB);

/* Start executing on the GPU */

kernel <<<gridDim, blockDim>>>

(a_device, b_device);

/* Copy values from device back to host */

cudaMemcpy (b_host, b_device, size,

cudaMemcpyDeviceToHost);

}

```

Fig. 2. Example Code: Base Case

general-purpose applications to be ported easily onto the GPU. A straightforward implementation of an application would be to utilize only global memory as a proof of concept for parallelizing the algorithm on CUDA.

Figure 2 shows an example CUDA code. The function main sets up the data for computation on the CPU while the function kernel contains the code that is actually executed on the GPU. Notice that variables that reside in the global memory of the GPU, like a\_device, are allocated in main and data movement is also performed there via API calls to cudaMemcpy.

In the kernel function, each thread on the GPU traverses a different row of the 2-D array a, scaling each element by a thread specific value before storing into the corresponding location in array b. Since each TB must have the same number of threads, depending on the data size and program parallelization there may be excess threads that do not have data to operate on. The conditional check on line 12 that exits the kernel function before the loop handles these cases. This check becomes important as we attempt to utilize memory coalescing (Section 2.3).

# 2.2 Shared Memory

Shared memory is a small (16KB per SM for the GeForce 8800) readable and writable on-chip memory and as fast as register access. Shared memory is uninitialized at the beginning of execution, and resident data is private to each TB

and visible to all threads within the same TB. The intuition is that shared memory should be used for data that is reused, especially if reused across different threads in a TB. However, we found that memory performance improvement from coalesced global memory accesses (Section 2.3) is large enough that shared memory should be leveraged for such purposes even if there is no data reuse.

# 2.3 Memory Coalescing

Global memory does have a behavior called *memory coalescing* that helps conserve bandwidth while reducing effective latency. Conceptually it is similar to loading an entire cache line from memory versus loading one word at a time. Threads in a TB are numbered along the x direction first and gathered sequentially into *warps*. On the GeForce 8800 a group of 32 threads form a warp. Each warp executes in SIMD (single-instruction, multiple-data) fashion, i.e. all threads in the same warp execute the same instruction at the same time. When the threads of a half-warp execute a global load, the loads are consolidated if they meet constraints necessary for the hardware to perform memory coalescing. Otherwise the loads are serviced individually. We summarize the requirements here and refer interested readers to [10] for full details.

There are four major requirements that memory accesses to global memory have to follow for memory coalescing to happen:

- 1. Each element of the array has to be 4, 8, or 16 bytes and aligned.

- 2. The threads in the half-warp have to access consecutive memory addresses in order, e.g. thread number N within the half-warp need to access address BaseAddr + N.

- 3. Thread numbering matters only along the first dimension of the thread block, the x dimension.  $^1$

- 4. BaseAddr must be aligned to a multiple of the element size.

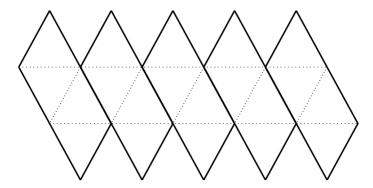

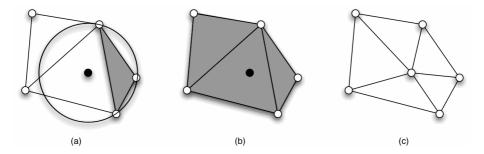

Fig. 3. Graphical View of Data Traversal: (a) Row (b) Column (c) Tiled

<sup>&</sup>lt;sup>1</sup> Thread blocks are usually created so that the x dimension is a multiple of the number of threads in a warp.

The requirements for memory coalescing are complex. Furthermore, with the exception of access alignment, all of the requirements must be fulfilled or there will be no improvement in the memory performance; a partial improvement usually occurs if alignment is the only requirement missed. The data access pattern to fulfill the memory coalescing requirement is also not natural for all algorithms, e.g. reduction across the rows of an array. When performing a reduction across the rows of an array, it is more natural to have one thread per row, as in Figure 3(a). The different groups of colored arrows represent different TBs. However, traversing one thread per column, shown in Figure 3(b), is needed to fulfill requirement 2 for memory coalescing. The data accessed by threads in a half-warp need to be adjacent to one another in the horizontal direction, not vertical, for the accesses to coalesce. The lack of synchronization across TBs also contributes to making this traversal pattern unnatural for performing a reduction across rows in CUDA. An alternative is to tile the computation, as shown in Figure 3(c). The tile is first traversed along the column and data is coalesced loaded into a buffer in shared memory, indicated by the grayed arrows. The algorithm then operates on the data along the row from shared memory before moving to the next tile. The performance improvement from doing coalesced loads and using shared memory makes this worthwhile despite the instruction overhead.

For example, the memory access to array a on line 18 of Figure 2 does not coalesce because it violates rule number 2. For each iteration of the loop, thread N accesses a [N\*ASIZE + i]; bki does not matter since the threads are in the same thread block. This means that each thread is accessing data vertically adjacent to each other, as in Figure 3(a), which does not trigger coalescing.

Figure 4 shows the kernel code from Figure 2 rewritten by hand so the algorithm is tiled and the memory accesses coalesced. The amount of code is roughly doubled. The original loop has been tiled and additional code is inserted to load/store data between global and shared memory. The load from array a on line 25 is coalesced since thread N accesses a [k\*ASIZE + N] on each iteration. The computation kernel now operates on the data in shared memory, and the loop around it has included the check on line 12 of the original code as an additional condition. In other words, the excess threads we mentioned back in Section 2.1 may be used to perform memory coalescing accesses, but must not be allowed to perform actual computation.

This rewriting is a large additional burden on the programmer. Not only must the programmer fulfill the memory coalescing requirements, the programmer also has to maintain correctness. The performance improvement this optimization provides will be the ideal, or oracle, case for CUDA-lite.

# 3 CUDA-Lite

Since the behavior of memory coalescing is complex yet understood, we believe that such transformations are best undertaken by an automated tool. This would reduce the potential for errors in writing memory coalescing code, and reduce the burden upon programmers. In our vision, programmers would provide a

straightforward implementation of the kernel code that utilizes only global memory, and depend on tools to optimize the memory performance.

We have developed tools to automate the transformations previously done by hand to maximize memory performance via memory coalescing. The programmer provides a version of the program that has been parallelized for CUDA using only global memory and the tools output a version with the memory accesses optimized. In other words, the tools transform code like the kernel function in Figure 2 to the memory coalescing version in Figure 4. We rely upon information

```

#define ASIZE 3000

#define TPB 32

global

void

kernel (float *a, float *b)

int thi = threadIdx.x;

int bki = blockIdx.x;

float t = (float) thi + bki;

10

int i;

int j, End, k;

_shared__ float a_shared[TPB][TPB];

float b_shared[TPB][TPB];

15

End = ASIZE % TPB == 0 ? ASIZE /

(ASIZE/TPB)+1;

(j = 0; j < End; j++)

/* Coalesce loads */

20

syncthreads();

for (k = 0; k < TPB; k++)

if ((j*TPB + thi < ASIZE) &&

((bki*TPB+k)*ASIZE + j*TPB + thi < ASIZE * ASIZE))

25

a_shared[k][thi] = a[(bki*TPB + k)*ASIZE + j*TPB + thi];

syncthreads();

/* Conditions:

30

* TPB && obey original end && !(early exit condition)

*/

for (i = 0;

(i < TPB) && (j*TPB+i < ASIZE) && !(bki * TPB + thi >= ASIZE);

i++)

{

b_shared[thi][i] = a_shared[thi][i] * t;

}

/* Coalesce stores */

35

Coalesce stores

40

syncthreads();

for (k = 0; k < TPB; k++)

if ((j*TPB + thi < ASIZE) &&

((bki*TPB+k)*ASIZE + j*TPB + thi < ASIZE * ASIZE))

b[(bki*TPB + k)*ASIZE + j*TPB + thi] = b_shared[k][thi];

45

syncthreads();

49 }

```

Fig. 4. Example Code: Hand Coalesced Kernel

```

(a) __annotation (L"__global__ <threads per block> <thread blocks per SM>");

(b) __annotation (L"garray <name> <rank> <element size> <rank sizes>");

(c) __annotation (L"BoundChk");

(d) annotation (L"loop <iterator> <start> <end> <increment>");

```

Fig. 5. CUDA-lite Annotations

from the programmer provided via annotations to perform our transformations. We call the software tools and annotations together *CUDA-lite*.

Figure 5 shows the current form of the annotations in CUDA-lite. Part (a) indicates the functions of interest, i.e. kernel functions running on the GPU, and parallelization factors. While some of the information, like threads per TB, can eventually be derived from CUDA code, the last argument gives programmers some control over how much resources a kernel generated by CUDA-lite should take. Part (b) indicates what arrays in global memory are of interest and their properties. This gives control over which memory accesses are targeted for optimization, which uses up resources. The speedup gained from performing memory coalescing needs to be balanced against excessive resource usage that reduces executing parallelism. We will discuss this in detail in Section 4. Part (c) is for annotating exit checks, such as the conditional check on line 12 of Figure 2 mentioned in Section 2.1. While CUDA threads may terminate early, CUDAlite may need those threads to satisfy memory coalescing and synchronization requirements. Therefore CUDA-lite removes the early termination and places guards around the original computation, as mentioned in Section 2.3. Finally, part (d) conveys information about the control flow of loops in the program. We currently use this information to perform loop transformations.

We recognize that some of the information provided by the annotations is derivable by advanced compiler techniques. However, the point of the annotations was to quickly provide the additional information needed and enable the transformations so that the memory hierarchy optimization automation work can proceed. It is not necessarily the final form.

Requirement 2 of the four requirements detailed in Section 2.3 is the most difficult to satisfy and check for. CUDA-lite derives the expression used in global memory accesses by performing a backwards dataflow up to the parameters of the kernel function and thread indices. The expression is first simplified by extracting all references to the thread index in the x direction. We leverage the SIMD execution model to eliminate the need for temporal locality checks, since the execution model guarantees that the expression is the same for all threads in the warp. The desired expression is one where every thread in a half-warp accesses the same location, differing only by their order within the half-warp. Consequently, any instance of  $\lfloor thi.x/hwarp \rfloor$  can be safely disregarded, where thi.x is the thread index in the x dimension and hwarp is the number of threads in a half-warp. Mathematically this can be seen as the function f in Equation 1.

As long as the expression fits the form of the function, then the memory access is coalesced.

$f(thi.x) = thi.x + g\left(\left\lfloor \frac{thi.x}{hwarp} \right\rfloor\right) + C \tag{1}$

Figure 6(a) shows the relevant pseudo-code and expression generated by CUDA-lite for the memory access to array a in Figure 2. Due to the ASIZE multiplier on the first term, the expression does not fit function f and thus the load is not coalesced. Part (b) shows the memory access to array a in Figure 4. Unlike part (a), the expression does fit the form of the function f and therefore the access is coalesced.

If the memory access is not already coalesced, CUDA-lite will attempt to automatically generate a coalescing version. The labels of the additional boxes in Figure 4 outline the majority of the transformations: inserting shared memory variables, performing loop tiling, generating memory coalesced loads and/or stores, and replacing the original global memory accesses with accesses to the corresponding data in shared memory.

The shared memory size and tiling factor are fixed and known for each target GPU, due to the half-warp requirement for memory coalescing. The amount of shared memory allocated can thus be determined by the number of arrays of interest, array dimensions, and array element size. The generation of coalescing loads or stores depends on the relationship between the array dimension and the threading dimension. If they match, then CUDA-lite needs to have each thread load from the appropriate place in global memory into the thread's corresponding position in shared memory. If the array is of higher dimension than the thread organization, two-dimension to one dimension in the running example, then CUDA-lite generates loops that load/store the data. This can be seen in the Coalesced Loads and Stores boxes of Figure 4. These loops must not only be tiled correctly for correct data movement but they must also obey the array bounds.

Fig. 6. Array Access and Expression (a) Non-Coalescing (b) Coalescing

```

#define ASIZE 3000

#define TPB 32

kernel (float *a, float *b)

_annotation (L"_global__ TPB 1");

_annotation (L"garray a 2 4 ASIZE ASIZE'

_annotation (L"garray b 2 4 ASIZE ASIZE'

int thi = threadIdx.xx

int bki = blockIdx.x;

float t = (float) thi + bki;

int i;

15

__annotation (L"BoundChk");

if (bki * TPB + thi >= ASIZE)

return;

for (i = 0; i < ASIZE; i++)

__annotation (L"loop i 0 ASIZE 1");

b[(bki*TPB+thi)*ASIZE + i]

a[(bki*TPB+thi)*ASIZE + i] * t;

25

```

Fig. 7. Example Code: CUDA-lite Kernel

Figure 7 shows how the example kernel would be annotated using the current implementation of CUDA-lite. The programmer only needs to insert the five boxed additional lines instead of doubling the amount of code like in Figure 4.

It is important to note that CUDA-lite does not affect parallelization and threading decisions, and operates under the constraints of how the program has been parallelized. This was a deliberate decision to make the problems that CUDA-lite is tackling more tractable. CUDA-lite can be folded into a more comprehensive programming framework for GPU computing system as the part that handles memory optimization.

# 4 Experimental Results

We have implemented CUDA-lite using the Phoenix compiler [7] as a source-to-source compiler using two Phoenix plug-ins: one to perform the necessary analysis and code transformations, and another to generate source code back from the IR. The regenerated source code is then fed into NVIDIA's compiler nvcc to generate binaries for execution. We used CUDA version 1.0 for all of our experiments. The CPU was an Opteron 248 system running at 2.2GHz with 1GB of memory. The GPU was a GeForce 8800 GTX. The source codes for Phoenix are straightforward CUDA implementations that use only global memory, with slight manipulations so the CUDA extensions not recognized by Phoenix can be passed through and regenerated correctly.

We present three applications as our benchmark: MRI-FHD, TPACF, and the running example of this paper. These three applications display differences in the arrays to be optimized (e.g. 1-D and 2-D) and the level of control flow sophistication (e.g. loop nesting) that CUDA-lite had to handle. MRI-FHD is one of the compute intensive portions of three-dimensional MRI Reconstruction, of which details can be found in [16]. TPACF stands for the two-point angular

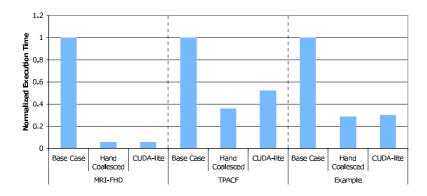

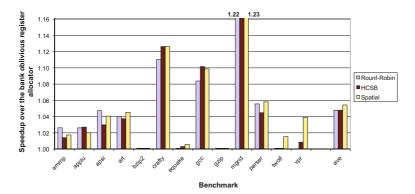

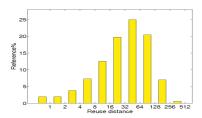

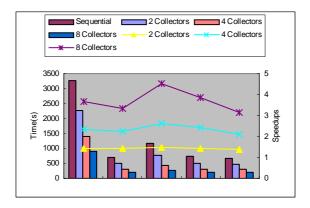

Fig. 8. Overall Results

correlation function, which is used to characterize the probability of finding a cosmological object at a given distance from another cosmological body. A more detailed description of the algorithm can be found in [3]. Both of these programs experienced terrific speedup moving from CPU to GPU [14].

Figure 8 shows the overall results for our benchmarks. The run times are normalized to the base case of the application implemented in CUDA utilizing only global memory. For each application we show base, hand-coalesced, and CUDA-lite results. It is obvious how important improving the memory performance can be, providing between 2 to 17x performance difference in these studies. CUDA-lite, despite being generated from an automated tool, provided performance comparable to the hand-generated versions for all of the applications. We explain the discrepancy of the results between hand-generated and CUDA-lite-generated code in Section 4.1.

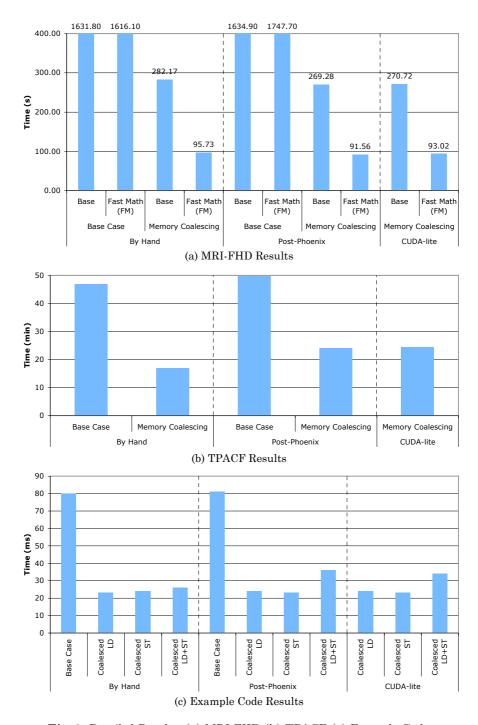

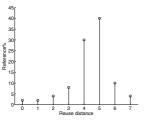

Figure 9 shows the detailed results of our experiments. Part (a) is MRI-FHD. Fast math is a compiler option in nvcc to utilize the hardware special function units (SFUs) on the GeForce 8800. This is very beneficial for MRI-FHD because its sine and cosine calculations can be performed on the SFUs. We present three sets of data: Code generated by hand, passing hand-generated code through Phoenix (Post-Phoenix), and CUDA-lite. The second set of data gives an idea of the overhead for going through a translation tool, and provides a more appropriate comparison for CUDA-lite. Note that Post-Phoenix and CUDA-lite memory coalescing code out-perform hand-generated. Fewer registers per thread were allocated by nvcc for the Post-Phoenix and CUDA-lite codes than the hand-generated code, which allowed two TBs to run concurrently on an SM. Otherwise the register allocation allowed only one. Part(b) shows the details of the TPACF results. Although the performance of CUDA-lite is the same as Post-Phoenix, they are both worse than hand-generated. Only one TB could run on an SM at a time in all cases due to shared memory usage.

Figure 9(c) shows the results for the running example code in this paper. We compare the benefits of load coalescing, store coalescing, and both. There are

Fig. 9. Detailed Results: (a) MRI-FHD (b) TPACF (c) Example Code

two arrays in the example code. Array a is read while array b is stored to. Using the annotations in CUDA-lite, we control which accesses are coalesced by the tool. The results indicate that coalescing either the load or the store is better than coalescing both. When only one access to one array is coalesced, up to three TBs can run concurrently on an SM. When accesses to both arrays are coalesced, the amount of shared memory used is doubled and the number of TBs running is reduced to one. Consequently, automatically coalescing all memory accesses is not always a good policy. Resource usage and overall performance need to be taken into account, perhaps in a performance optimization search like in [15].

# 4.1 Post-phoenix Overhead

Intuitively, regenerating source code from a compiler should add some amount of overhead. Curiously, our results show that this does not always translate into performance loss. Going through Phoenix showed no ill effect for MRI-FHD, a visible slowdown in TPACF, and mixed results in the example code. We narrowed down the problem to a combination of control flow and executing parallelism.

The output of Phoenix uses only GOTO statements to express the control flow of the program. This results in poor performance on CUDA. We verified this by manually generating versions that consist of only GOTO statements for control flow and observed similar degradations in performance. This explains the slowdown of TPACF and coalesced LD+ST in the example code. Multiple TBs executing on an SM provides additional parallelism to mask this overhead in MRI-FHD.

# 5 Related Work

Techniques have been proposed to allow array-dominated applications to benefit from scratch-pad memories [5,12]. In [2], the authors used the polyhedral model to detect data locality and copy the portion of data that is going to be used in a tile into the shared memory (or "scratch-pad memory") of a GPU. Our motivation and approach is different as we copy data from global memory to shared memory even if there is no data reuse. This is due to the significant performance benefit of coalescing global memory accesses on the GPU architecture.

Related techniques have also been developed to manipulate data accesses for SIMD devices [13,18]. SIMD units typically operate on short vectors, as opposed to the large massively parallel arrays that CUDA prefers. Also, memory coalescing has to be linear access since that is the requirement from the programming model. Data permutation and rearrangement would apply to setting up the data outside of the GPU kernel, or detecting that the data usage within the kernel covers data in such a way that interaction with the array should be coalesced.

We performed loop transformations such as tiling to properly reorganize the execution pattern. Wolf et al. [17] covered the loop transformations that enhance

data locality in loop nests. We decided not to automate the tiling transformations and rely upon programmer annotations instead since that was not the focus of our work. Our approach is not the same as the multi-level tiling schemes presented in [4,6], but we share the view that having a global knowledge of data access patterns facilitates improving locality in higher levels of memory hierarchy and increases global memory bandwidth performance.

There exists a body of work that incorporates programmer knowledge in performing transformations. Among these, the Spec# system by Microsoft [1] is closest to our work. It utilizes annotations to allow a separate verifying compiler to check for program correctness. Our annotations are information that feed directly into compiler analyses and transformations, usually information that would otherwise be missing or difficult to infer automatically by the compiler.

# 6 Conclusion and Future Work

In this paper we introduced CUDA-lite to help relieve programmers of the burden of optimizing the memory performance of code developed under the CUDA programming environment for GPU, which offers a complex memory hierarchy that needs to be leveraged to best match memory bandwidth with compute throughput. This is an important task due to the large effect memory performance has on overall performance (2-17x).

We show that CUDA-lite produces code with performance comparable to hand-coded versions. The coding requirements for CUDA-lite are lower than performing the same transformations by hand and provides a layer of abstraction from the definition of warps in CUDA, which could change in the future. Since CUDA-lite does not handle the parallelizing aspects of GPU programming, we foresee CUDA-lite as the memory optimizing module of an eventual overall framework for facilitating GPGPU programming that encompasses parallelization and resource usage decisions to maximize performance.

For future work we plan to broaden the application set and to extend CUDA-lite to leverage constant memory. We also hope to simplify the annotations in CUDA-lite, some of which can be replaced by compiler analyses currently not in our infrastructure.

# Acknowledgment

We would like to thank David Kirk and NVIDIA for generous hardware loans and support. We also thank the anonymous reviewers for their feedback. The authors acknowledge the support of the Gigascale Systems Research Center, funded under the Focus Center Research Program, a Semiconductor Research Corporation program. Experiments were made possible by NSF CNS grant 05-51665. Any opinions, findings, conclusions, or recommendations expressed in this publication are those of the authors and do not necessarily reflect the views of the NSF. This work was performed with software donations from Microsoft.

# References

- 1. Barnett, M., Leino, K.R.M., Schulte, W.: The Spec# programming system: An overview. In: Barthe, G., Burdy, L., Huisman, M., Lanet, J.-L., Muntean, T. (eds.) CASSIS 2004. LNCS, vol. 3362, pp. 49–69. Springer, Heidelberg (2005)

- Baskaran, M.M., Bondhugula, U., Krishnamoorthy, S., Ramanujam, J., Rountev, A., Sadayappan, P.: Automatic data movement and computation mapping for multi-level parallel architectures with explicitly managed memories. In: PPoPP 2008: Proceedings of the 13th ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming (2008)

- 3. Brunner, R.J., Kindratenko, V.V., Myers, A.D.: Developing and deploying advanced algorithms to novel supercomputing hardware. In: Proceedings of NASA Science Technology Conference NCTC 2007 (2007)

- 4. Guo, J., Bikshandi, G., Fraguela, B.B., Garzaran, M.J., Padua, D.: Programming with tiles. In: PPoPP 2008: Proceedings of the 13th ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming (2008)

- Kandemir, M., Choudhary, A.: Compiler-directed scratch pad memory hierarchy design and management. In: DAC 2002: Proceedings of the 39th Conference on Design Automation (2002)

- Knight, T.J., Park, J.Y., Ren, M., Mike, H., Erez, M., Fatahalian, K., Aiken, A., Dally, W.J., Hanrahan, P.: Compilation for explicitly managed memory hierarchies. In: Proceedings of the 2007 ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming (2007)

- 7. Microsoft. Phoenix compiler, http://research.microsoft.com/Phoenix/

- 8. Nickolls, J., Buck, I.: NVIDIA CUDA software and GPU parallel computing architecture. Microprocessor Forum (May 2007)

- 9. NVIDIA. NVIDIA CUDA, http://www.nvidia.com/cuda

- 10. NVIDIA. NVIDIA CUDA Compute Unified Device Architecture Programming Guide: Version 1.0. NVIDIA Corporation (June 2007)

- 11. Owens, J.D., Luebke, D., Govindaraju, N., Harris, M., Krüger, J., Lefohn, A.E., Purcell, T.J.: A survey of general-purpose computation on graphics hardware. Computer Graphics Forum 26(1), 80–113 (2007)

- Panda, P.R., Dutt, N.D., Nicolau, A.: Efficient utilization of scratch-pad memory in embedded processor applications. In: EDTC 1997: Proceedings of the 1997 European Conference on Design and Test (1997)

- 13. Ren, G., Wu, P., Padua, D.A.: Optimizing data permutations for SIMD devices. In: PLDI, pp. 118–131 (2006)

- 14. Ryoo, S., Rodrigues, C.I., Baghsorkhi, S.S., Stone, S.S., Kirk, D.B., Hwu, W.W.: Optimization principles and application performance evaluation of a multithreaded GPU using CUDA. In: PPoPP, pp. 73–82 (2008)

- Ryoo, S., Rodrigues, C.I., Stone, S.S., Baghsorkhi, S.S., Ueng, S., Stratton, J.A., Hwu, W.W.: Program optimization space pruning for a multithreaded GPU. In: CGO (April 2008)

- Stone, S.S., Haldar, J.P., Tsao, S.C., Hwu, W.W., Liang, Z., Sutton, B.P.: Accelerating advanced MRI reconstructions on GPUs. In: Proceedings of the 2008 International Conference on Computing Frontiers (May 2008)

- 17. Wolf, M.E., Lam, M.S.: A data locality optimizing algorithm. In: PLDI 1991: Proceedings of the ACM SIGPLAN 1991 Conference on Programming Language Design and Implementation (1991)

- 18. Wu, P., Eichenberger, A.E., Wang, A., Zhao, P.: An integrated simdization framework using virtual vectors. In: ICS, pp. 169–178 (2005)

# MCUDA: An Efficient Implementation of CUDA Kernels for Multi-core CPUs

John A. Stratton, Sam S. Stone, and Wen-mei W. Hwu

Center for Reliable and High-Performance Computing and Department of Electrical and Computer Engineering University of Illinois at Urbana-Champaign {stratton,ssstone2,hwu}@crhc.uiuc.edu

Abstract. CUDA is a data parallel programming model that supports several key abstractions - thread blocks, hierarchical memory and barrier synchronization - for writing applications. This model has proven effective in programming GPUs. In this paper we describe a framework called MCUDA, which allows CUDA programs to be executed efficiently on shared memory, multi-core CPUs. Our framework consists of a set of source-level compiler transformations and a runtime system for parallel execution. Preserving program semantics, the compiler transforms threaded SPMD functions into explicit loops, performs fission to eliminate barrier synchronizations, and converts scalar references to thread-local data to replicated vector references. We describe an implementation of this framework and demonstrate performance approaching that achievable from manually parallelized and optimized C code. With these results, we argue that CUDA can be an effective data-parallel programming model for more than just GPU architectures.

### 1 Introduction

In February of 2007, NVIDIA released the CUDA programming model for use with their GPUs to make them available for general purpose application programming [1]. However, the adoption of the CUDA programming model has been limited to those programmers willing to write specialized code that only executes on certain GPU devices. This is undesirable, as programmers who have invested the effort to write a general-purpose application in a data-parallel programming language for a GPU should not have to make an entirely separate programming effort to effectively parallelize the application across multiple CPU cores.

One might argue that CUDA's exposure of specialized GPU features limits the efficient execution of CUDA kernels to GPUs. For example, in a typical usage case of the CUDA programming model, programmers specify hundreds to thousands of small, simultaneously active threads to achieve full utilization of GPU execution resources. However, a current CPU architecture currently supports only up to tens of active thread contexts. On the other hand, some language features in the CUDA model can be beneficial to performance on a CPU, because these features encourage the programmer to use more disciplined

control flow and expose data locality. Section 2 describes in more detail the key CUDA language features and a deeper assessment of why we expect many CUDA features to map well to a CPU architecture for execution. We propose that if an effective mapping of the CUDA programming model to a CPU architecture is feasible, it would entail translations applied to a CUDA program such that the limiting features of the programming model are removed or mitigated, while the beneficial features remain exposed when possible.

Section 3 describes how the MCUDA system translates a CUDA program into an efficient parallel C program. Groups of individual CUDA threads are collected into a single CPU thread while still obeying the scheduling restrictions of barrier synchronization points within the CUDA program. The data locality and regular control encouraged by the CUDA programming model are maintained through the translation, making the resulting C program well suited for a CPU architecture.

The implementation and experimental evaluation of the MCUDA system is presented in Section 4. Our experiments show that optimized CUDA kernels utilizing MCUDA achieve near-perfect scaling with the number of CPU cores, and performance comparable to hand-optimized multithreaded C programs. We conclude this paper with a discussion of related work in Section 5 and some closing observations in Section 6.

# 2 Programming Model Background

On the surface, most features included in the CUDA programming model seem relevant only to a specific GPU architecture. The primary parallel construct is a data-parallel, SPMD kernel function. A kernel function invocation explicitly creates many CUDA threads (hereafter referred to as logical threads.) The threads are organized into multidimensional arrays that can synchronize and quickly share data, called thread blocks. These thread blocks are further grouped into another multidimensional array called a grid. Logical threads within a block are distinguished by an implicitly defined variable threadIdx, while blocks within a grid are similarly distinguished by the implicit variable blockIdx. At a kernel invocation, the programmer uses language extensions to specify runtime values for each dimension of threads in a thread block and each dimension of thread blocks in the grid, accessible within the kernel function through the variables blockDim and gridDim respectively. In the GPU architecture, these independent thread blocks are dynamically assigned to parallel processing units, where the logical threads are instantiated by hardware threading mechanisms and executed.

Logical threads within CUDA thread blocks may have fine-grained execution ordering constraints imposed by the programmer through barrier synchronization intrinsics. Frequent fine-grained synchronization and data sharing between potentially hundreds of threads is a pattern in which CPU architectures typically do not achieve good performance. However, the CUDA programming model does restrict barrier synchronization to within thread blocks, while different thread blocks can be executed in parallel without ordering constraints.

The CUDA model also includes explicitly differentiated memory spaces to take advantage of specialized hardware memory resources, a significant departure from the unified memory space of CPUs. The *constant* memory space uses a small cache of a few kilobytes optimized for high temporal locality and accesses by large numbers of threads across multiple thread blocks. The *shared* memory space maps to the scratchpad memory of the GPU, and is shared among threads in a thread block. The *texture* memory space uses the GPU's texture caching and filtering capabilities, and is best utilized with data access patterns exhibiting 2-D locality. More detailed information about GPU architecture and how features of the CUDA model affect application performance is presented in [2].

In the CUDA model, logical threads within a thread block can have independent control flow through the program. However, the NVIDIA G80 GPU architecture executes logical threads in SIMD bundles called warps, while allowing for divergence of thread execution using a stack-based reconvergence algorithm with masked execution [3]. Therefore, logical threads with highly irregular control flow execute with greatly reduced efficiency compared to a warp of logical threads with identical control flow. CUDA programmers are strongly encouraged to adopt algorithms that force logical threads within a thread block to have very similar, if not exactly equivalent, execution traces to effectively use the implicitly SIMD hardware effectively. In addition, the CUDA model encourages data locality and reuse for good performance on the GPU. Accesses to the global memory space incur uniformly high latency, encouraging the programmer to use regular, localized accesses through the scratchpad shared memory or the cached constant and texture memory spaces.

A closer viewing of the CUDA programming model suggests that there could also be an efficient mapping of the execution specified onto a current multicore CPU architecture. At the largest granularity of parallelism within a kernel, blocks can execute completely independently. Thus, if all logical threads within a block occupy the same CPU core, there is no need for inter-core synchronization during the execution of blocks. Thread blocks often have very regular control flow patterns among constituent logical threads, making them amenable to the SIMD instructions common in current x86 processors [4,5]. In addition, thread blocks often have the most frequently referenced data specifically stored in a set of thread-local or block-shared memory locations, which are sized such that they approximately fit within a CPU core's L1 data cache. Shared data for the entire kernel is often placed in constant memory with a size limit appropriate for an L2 cache, which is frequently shared among cores in CPU architectures. If a translation can be designed such that these attributes are maintained, it should be possible to generate effective multithreaded CPU code from the CUDA specification of a program.

### 3 Kernel Translation

While the features of the model seem promising, the mapping of the computation is not straightforward. The conceptually easiest implementation is to spawn an

OS thread for every GPU thread specified in the programming model. However, allowing logical threads within a block to execute on any available CPU core mitigates the locality benefits noted in the previous section, and incurs a large amount of scheduling overhead. Therefore, we propose a method of translating the CUDA program such that the mapping of programming constructs maintains the locality expressed in the programming model with existing operating system and hardware features.

There are several challenging goals in effectively translating CUDA applications. First, each thread block should be scheduled to a single core for locality, yet maintain the ordering semantics imposed by potential barrier synchronization points. Without modifying the operating system or architecture, this means the compiler must somehow manage the execution of logical threads in the code explicitly. Second, the SIMD-like nature of the logical threads in many applications should be clearly exposed to the compiler. However, this goal is in conflict with supporting arbitrary control flow among logical threads. Finally, in a typical load-store architecture, private storage space for every thread requires extra instructions to move data in and out of the register file. Reducing this overhead requires identifying storage that can be safely reused for each thread.

The translation component of MCUDA which addresses these goals is composed of three transformation stages: iterative wrapping, synchronization enforcement, and data buffering. For purposes of clarity, we consider only the case of a single kernel function with no function calls to other procedures, possibly through exhaustive inlining. It is possible to extend the framework to handle function calls with an interprocedural analysis, but this is left for future work. In addition, without loss of generality, we assume that the code does not contain goto or switch statements, possibly through prior transformation [6]. All transformations presented in this paper are performed on the program's abstract syntax tree (AST).

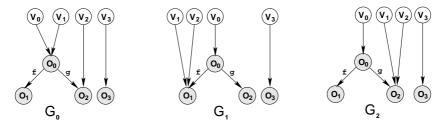

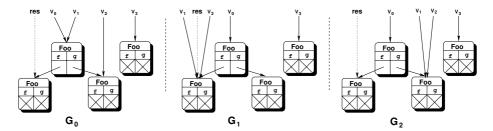

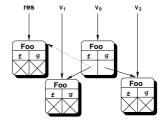

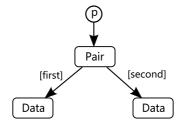

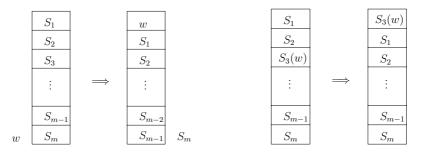

# 3.1 Transforming a Thread Block into a Serial Function

The first step in the transformation changes the nature of the kernel function from a per-thread code specification to a per-block code specification, temporarily ignoring any potential synchronization between threads. Figure 1 shows an example kernel function before and after this transformation. Execution of logical threads is serialized using nested loops around the body of the kernel function to execute each thread in turn. The loops enumerate the values of the previously implicit threadIdx variable and perform a logical thread's execution of the enclosed statements on each iteration. For the remainder of the paper, we will consider this introduced iterative structure a thread loop. Local variables are reused on each iteration, since only a single logical thread is active at any time. Shared variables still exist and persist across loop iterations, visible to all logical threads. The other implicit variables must be provided to the function at runtime, and are therefore added to the parameter list of the function.

By introducing a thread loop around a set of statements, we are making several explicit assumptions about that set of statements. The first is that the

```

void cengery(numatoms, gridspacing, energygrid[]) void cengery(numatoms, gridspacing, energygrid[],

blockDim, blockIdx, gridDim)

int x - blockIdx.x * blockDim.x

+ threadIdx.x;

dim3 threadIdx;

int y - blockIdx.y * blockDim.y

// Thread Loop

+ threadIdx.y;

for (threadIdx.y = 0;

int outIdx - gridDim.x * blockDim.x * y

threadIdx.y < blockDim.y;

threadIdx.y++)

+ x;

for (threadIdx.x = 0;

threadIdx.x < blockDim.x:

float energy - 0.0;

int atomid-0:

threadIdx.x++)

while(atomid<numatoms) {

{

int x = blockIdx.x * blockDim.x

+ threadIdx.x;

energygrid[outIdx] - energy;

int y - blockIdx.y * blockDim.y

+ threadIdx.v;

int outIdx - gridDim.x*blockDim.x * y

+ x;

float energy - 0.0;

int atomid-0:

while(atomid < numatoms) {

energygrid[outIdx] - energy;

// end Thread Loop;

```

Fig. 1. Introducing a thread loop to serialize logical threads in Coulombic Potential

program allows each logical thread to execute those statements without any synchronization between threads. The second is that there can be no side entries into or side exits out of the thread loop body. If the programmer has not specified any synchronization point and the function contains no explicit return statement, no further transformation is required, as a function cannot have side entry points, and full inlining has removed all side-exits. In the more general case, where using a single thread loop is insufficient for maintaining program semantics, we must partition the function into sets of statements which do satisfy these properties.

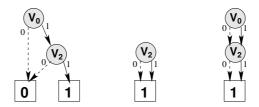

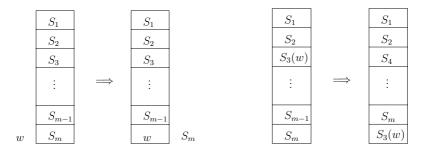

# 3.2 Enforcing Synchronization with Deep Fission

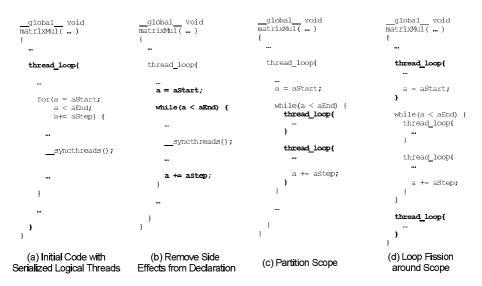

A thread loop implicitly introduces a barrier synchronization among logical threads at its boundaries. Each logical thread executes to the end of the thread loop, and then "suspends" until every other logical thread (iteration) completes the same set of statements. Therefore, a loop fission operation essentially partitions the statements of a thread loop into two sets of statements with an implicit barrier synchronization between them. A synchronization point found in the immediate scope of a thread loop can be thus enforced by applying a loop fission operation at the point of synchronization.

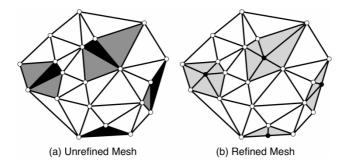

Although a loop fission operation applied to the thread loop enforces a barrier synchronization at that point, this operation can only be applied at the scope of the thread loop. As mentioned before, the general case requires a transformation that partitions statements into thread loops such that each thread loop contains no synchronization point, and each thread loop boundary is a valid synchronization point. For example, consider the case of Figure 2. There are at minimum four groups of statements required to satisfy the requirements for thread loops: one leading up to the for loop (including the loop initialization

Fig. 2. Applying deep fission in Matrix Multiplication to enforce synchronization

statement), one for the part of the loop before the synchronization point, one after the synchronization point within the loop (including the loop update), and finally the trailing statements after the loop.

In this new set of thread loops, the logical threads will implicitly synchronize every time the loop conditional is evaluated, in addition to the programmer-specified synchronization point. This is a valid transformation because of the CUDA programming model's requirement that control flow affecting a synchronization point must be thread-independent. This means that if the execution of a synchronization point is control-dependent on a condition, that condition must be thread-invariant. Therefore, if any thread arrives at the conditional evaluation, all threads must reach that evaluation, and furthermore must evaluate the conditional in the same way. Such a conditional can be evaluated outside of a thread loop once as a representative for all logical threads. In addition, it is valid to force all threads to synchronize at the point of evaluation, and thus safe to have thread loops bordering and comprising the body of the control structure.

In describing our algorithm for enforcing synchronization points, we first assume that all control structures have no side effects in their declarations. We enforce that *for* loops must be transformed into *while* loops in the AST, removing the initialization and update expressions. In addition, all conditional evaluations with side effects must be removed from the control structure's declaration, and assigned to a temporary variable, which then replaces the original condition in the control structure. Then, for each synchronization statement S, we apply Algorithm 1 to the AST with S as the input parameter.

After this algorithm has been applied with each of the programmer-specified synchronization points as input, the code may still have some control flow for which the algorithm has not properly accounted. Recall that thread loops assume

# Algorithm 1. Deep Fission around a Synchronization Statement S

#### loop

if Immediate scope containing S is not a thread loop then

Partition all statements within the scope containing S into thread loops. Statements before and after S form two thread loops. In the case of an if-else construct, this also means all statements within the side of the construct not containing S are formed into an additional thread loop. {See Figure 2(c)}

#### else

Apply a loop fission operation to the thread loop around S and return  $\{(See Figure 2(d).)\}$

#### end if

$S \leftarrow \text{Construct immediately containing } S \text{ {Parent of } S \text{ in the AST}}$

### end loop

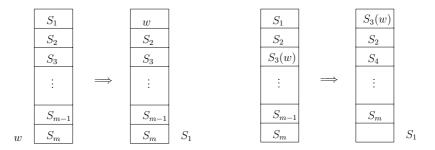

that there are no side entries or side exits within the thread loop body. Control flow statements such as *continue*, *break*, or *return* may not be handled correctly when the target of the control flow is not also within the thread loop. Figure 3(b) shows a case where irregular control flow would result in incorrect execution. In some iterations of the outer loop, all logical threads may avoid the break and synchronize correctly. In another iteration, all logical threads may take the break, avoiding synchronization. However, in the second case, control flow would leave the first thread loop before all logical threads had finished the first thread loop, inconsistent with the program's specification. Again, we note that since the synchronization point is control-dependent on the execution of the break statement, the break statement itself can be a valid synchronization point according to the programming model.

Therefore, the compiler must pass through the AST at least once more to identify these violating control flow statements. At the identification of a control flow statement S whose target is outside its containing thread loop, Algorithm 1 is once again applied, treating S as a synchronization statement. For the example of Figure 3, this results in the code shown in Figure 3(c). Since these

```

thread loop{

while() {

while() {

while() {

thread_loop{

thread_loop{

if()

if()

if()

break;

break;

break;

thread_loop{

syncthreads();

\\syncthreads();

thread_loop{

\\syncthreads();

thread_loop{

}

}

}

}

(c) Synchronized at

(a) Initial Code with

(b) Synchronized at

Serialized Logical Threads

Control Flow Point

Barrier Function

```

**Fig. 3.** Addressing unstructured control flow. The break statement is treated as an additional synchronization statement for correctness.

transformations more finely divide thread loops, they could reveal additional control flow structures that violate the thread loop properties. Therefore, this irregular control flow identification and synchronization step is applied iteratively until no additional violating control flow is identified.

The key insight is that we are not supporting arbitrary control flow among logical threads within a block, but leveraging the restrictions in the CUDA language to define a single-threaded ordering of the instructions of multiple threads which satisfies the partial ordering enforced by the synchronization points. This "over-synchronizing" allows us to completely implement a "threaded" control flow using only iterative constructs within the code itself. The explicit synchronization primitives may now be removed from the code, as they are guaranteed to be bounded by thread loops on either side, and contain no other computation. Because only barrier synchronization primitives are provided in the CUDA programming model, no further control-flow transformations to the kernel function are needed to ensure proper ordering of logical threads. Figure 4(a) shows the matrix multiplication kernel after this hierarchical synchronization procedure has been applied.

# 3.3 Replicating Thread-Local Data

Once the control flow has been restructured, the final task remaining is to buffer the declared variables as needed. Shared variables are declared once for the entire block, so their declarations simply need the *shared* keyword removed. However, each logical thread has a local store for variables, independent of all other logical threads. Because these logical threads no longer exist independently, the translated program must emulate private storage for logical threads within the block. The simplest implementation creates private storage for each thread's instance of the variable, analogous to scalar expansion [7]. This technique, which we call *universal replication*, fully emulates the local store of each logical thread by creating an array of values for each local variable, as shown in Figure 4(b). Statements within thread loops access these arrays by thread index to emulate the logical thread's local store.

However, universal replication is often unnecessary and inefficient. In functions with no synchronization, thread loops can completely serialize the execution of logical threads, reusing the same memory locations for local variables. Even in the presence of synchronization, some local variables may have live ranges completely contained within a thread loop. In this case, logical threads can still reuse the storage locations of those variables because a value of that variable is never referenced outside the thread loop in which it is defined. For example, in the case of Figure 4(b), the local variable k can be safely reused, because it is never live outside the third thread loop.

Therefore, to use less memory space, the MCUDA framework should only create arrays for local variables when necessary. A live-variable analysis determines which variables have a live value at the end of a thread loop, and creates arrays for those values only. This technique, called *selective replication*, results in the code shown in Figure 4(c), which allows all logical threads to use the same

```

__global__ void

matrixMul( float* C, float* A, float* B)

_global__void

matrixMul( float* C, float* A, float* B)

int a, b, c, aEnd, k;

int a[], b[], c[], aEnd[], k[];

float Csub;

__shared__ float As[16][16];

__shared__ float Bs[16][16];

float Csub[];

float As[16][16];

float Bs[16][16];

aEnd = Awidth * threadIdx.y + threadIdx.x;

a = Awidth * BLOCK_SIZE * blockIdx.y + aEnd;

b = BLOCK_SIZE * blockIdx.x;

aEnd[tid] = Awidth * threadIdx.y + threadIdx.x;

a[tid] = Awidth * BLOCK SIZE * blockIdx.y + aEnd[tid];

b[tid] = BLOCK_SIZE * blockIdx.x;

b[tid] = a[tid] + b[tid];

b[tid] = b[tid] + aEnd[tid];

b = a + b;

b = b + aEnd;

aEnd = a + Awidth;

Csub = 0;

aEnd[tid] = a[tid] + Awidth;

Csub[tid] = 0;

while (a < aEnd) {

while (a[0] < aEnd[0]) {

thread_loop{

As[threadIdx.y][threadIdx.x] = A[a];

thread_loop{

As[threadIdx.y][threadIdx.x] = A[a[tid]];

Bs[threadIdx.y][threadIdx.x] = B[b];

a += BLOCK SIZE;

Bs[threadIdx.y][tthreadIdx.x] = B[b[tid]];

a[tid] += BLCCK_SIZE;

b[tid] += BLCCK_SIZE*Bwidth;

b += BLOCK_SIZE*Bwidth;

thread_loop(

thread loop(

for (k = 0; k < BLOCK SIZE; k++)

Csub += As[threadIdx.y][k] *

for (k[tid] = 0; k[tid] < BLOCK_SIZE; k[tid]++)

Csub[tid] += As[threadIdx.y][k[tid]] *

Bs[k][threadIdx.x];

Bs[k[tid]][threadIdx.x];

thread_loop(

thread_loop{

C[c] = Csub;

C[c[tid]] = Csub[tid];

```

### (a) Synchronized Kernel

# (b) Universal Replication

```

_global__ void

matrixMul( float* C, float* A, float* B)

int a[], b[], c[], aEnd[], k;

float Csub[]:

float As[16][16];

float Bs[16][16];

nead_loop(

aEnd[tid] = Awidth * threadIdx.y + threadIdx.x;

a[tid] = Awidth * BLOCK_SIZE * blockIdx.y + aEnd[tid];

b[tid] = BLOCK_SIZE * blockIdx.x;

b[tid] = a[tid] + b[tid];

b[tid] = b[tid] + aEnd[tid];

aEnd[tid] = a[tid] + Awidth;

Csub[tid] = 0;

while (a[0] < aEnd[0]) {

thread loop{

As[threadIdx.y][threadIdx.x] = A[a[tid]];

Bs[threadIdx.y][tthreadIdx.x] = B[b[tid]];

a[tid] += BLOCK_SIZE;

b[tid] += BLOCK_SIZE*Bwidth;

thread_loop{

for (k = 0; k < BLOCK_SIZE; k++)

Csub[tid] += As[threadIdx.y][k]

Bs[k][threadIdx.x];

thread_loop{

C[c[tid]] = Csub[tid];

(c) Selective Replication

```

Fig. 4. Data replication in Matrix Multiplication

memory location for the local variable k. However, a and b are defined and used across thread loop boundaries, and must be stored into arrays.

References to a variable outside of the context of a thread loop can only exist in the conditional evaluations of control flow structures. Control structures must affect synchronization points to be outside a thread loop, and therefore must be uniform across the logical threads in the block. Since all logical threads should have the same logical value for conditional evaluation, we simply reference element zero as a representative, as exemplified by the while loop in Figure 4 (b-c).

It is useful to note that although CUDA defines separate memory spaces for the GPU architecture, all data resides in the same shared memory system in the MCUDA framework, including local variables. The primary purpose of the different memory spaces on the GPU is to specify access to the different caching mechanisms and the scratchpad memory. A typical CPU system provides a single, cached memory space, thus we map all CUDA memory types to this memory space.

#### 3.4 Work Distribution and Runtime Framework

At this point in the translation process the kernels are now defined as block-level functions, and all that remains is, on kernel invocation, to iterate through the block indexes specified and call the transformed function once for every specified block index. For a CPU that gains no benefits from multithreading, this is an efficient way of executing the kernel computation. However, CPU architectures that do gain performance benefits from multithreading will likely not achieve full efficiency with this method. Since these blocks can execute independently according to the programming model, the set of block indexes may be partitioned arbitrarily among concurrently executing OS threads. This allows the kernels to exploit the full block-level parallelism expressed in the programming model.

# 4 Implementation and Performance Analysis

We have implemented the MCUDA automatic kernel translation framework under the Cetus source-to-source compilation framework [8], with slight modifications to the IR and preprocessor to accept ANSI C with the language extensions of CUDA version 0.8. MCUDA implements the algorithms presented in the previous section for kernel transformations and applies them to the AST intermediate representation of Cetus. The live variable analysis required for robust selective replication described in Section 3.3 is incomplete, but the current implementation achieves the same liveness results for all the applications presented in this section. For compatibility with the Intel C Compiler (ICC), we replace the CUDA runtime library with a layer interfacing to standard libc functions for memory management. We chose to implement the runtime assignment of blocks to OS threads with OpenMP, using a single "parallel for" pragma to express the parallelism. A large existing body of work explores scheduling policies of such loops in OpenMP and other frameworks [9,10,11,12], For our experiments, we use the default compiler implementation.

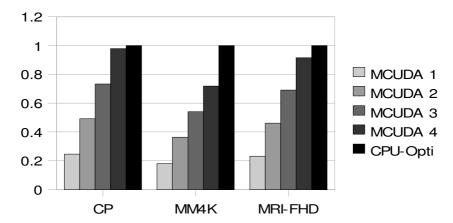

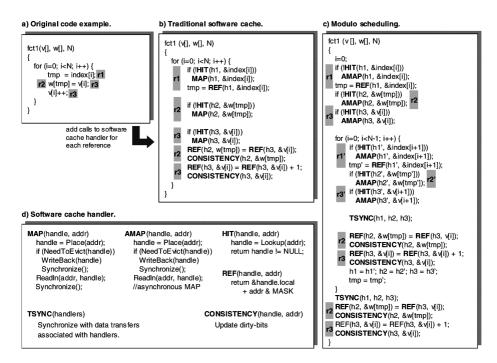

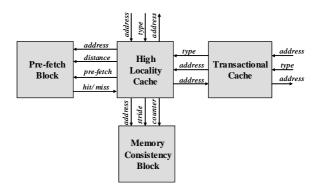

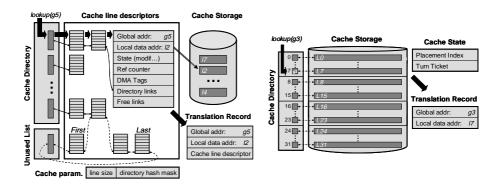

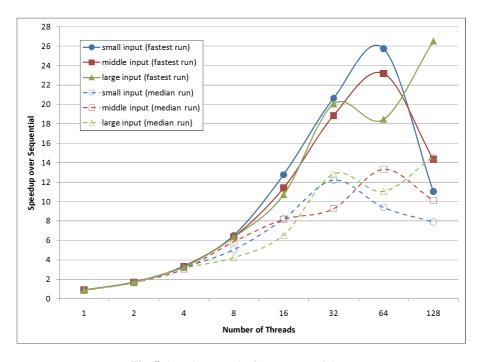

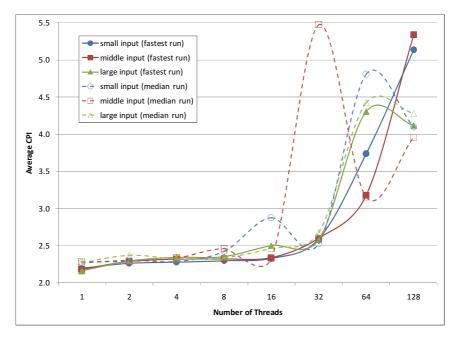

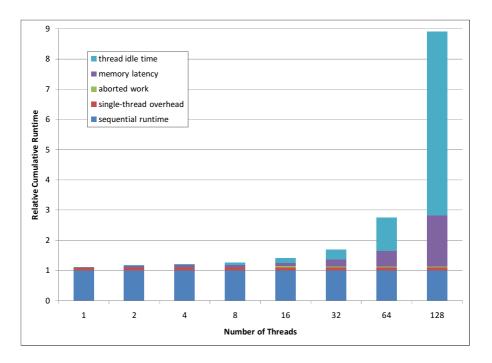

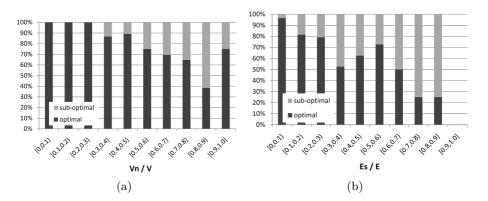

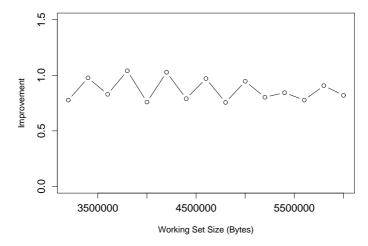

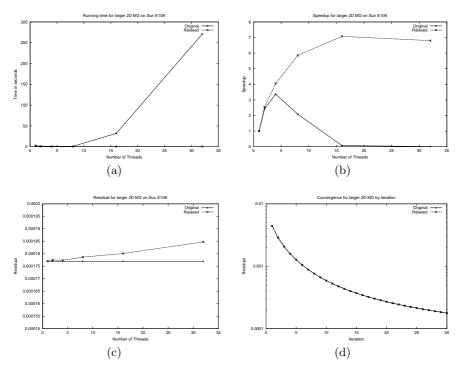

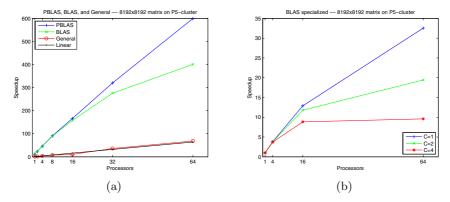

Figure 5 shows the kernel speedup of three applications: matrix multiplication of two 4kx4k element matrices (MM4K), Coulombic Potential (CP), and MRI-FHD, a computationally intensive part of high-resolution MRI image reconstruction. These applications have previously shown to have very efficient CUDA implementations on a GPU architecture [13]. The CPU baselines that

Fig. 5. Performance (inverse runtime) of MCUDA kernels relative to optimized CPU code. MCUDA results vary by the number of worker threads (1-4). CPU Opti implementations are parallelized across 4 threads.

we are measuring against are the most heavily optimized CPU implementations available to us, and are threaded by hand to make use of multiple CPU cores. All performance data was obtained on an Intel Core 2 Quad processor clocked at 2.66 GHz (CPU model Q6700). All benchmarks were compiled with ICC (version 10.1). Additionally, the CPU optimized matrix multiplication application uses the Intel MKL.

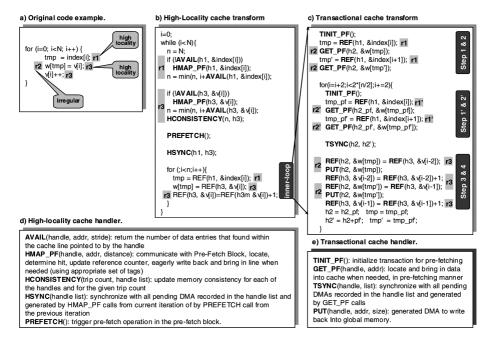

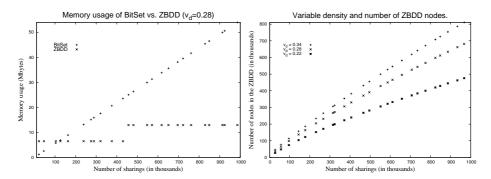

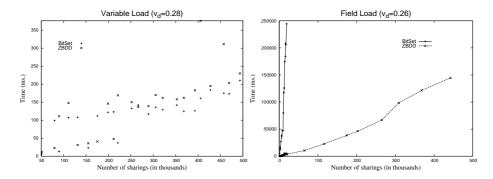

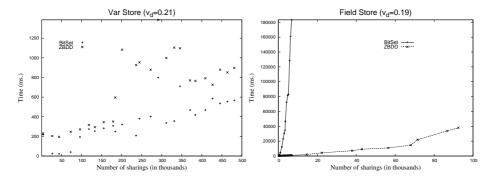

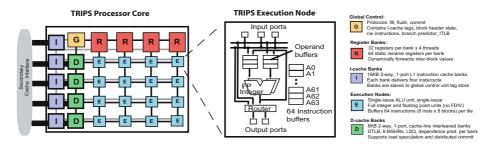

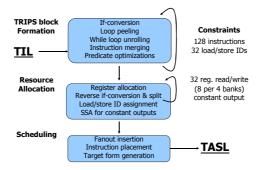

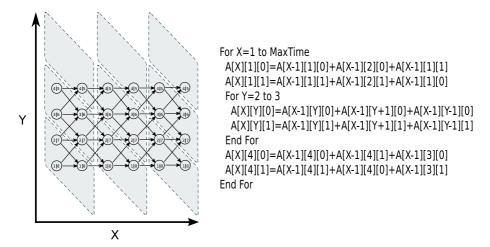

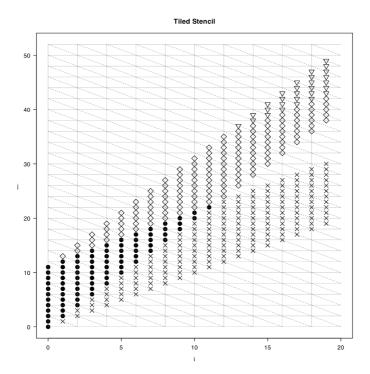

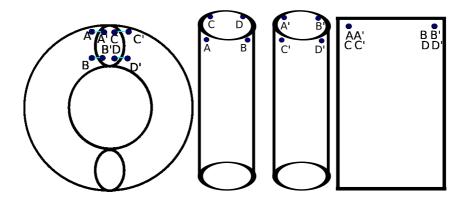

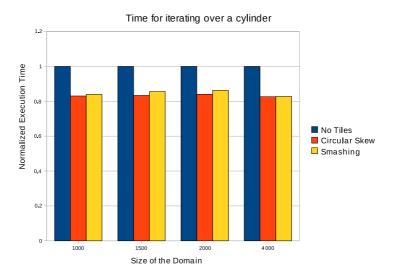

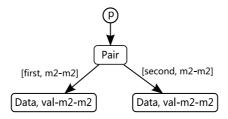

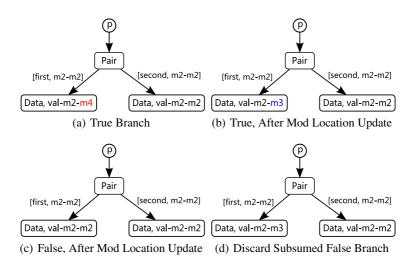

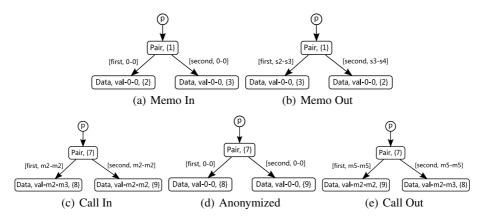

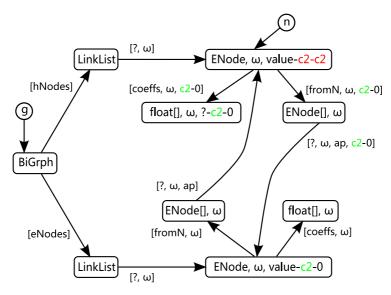

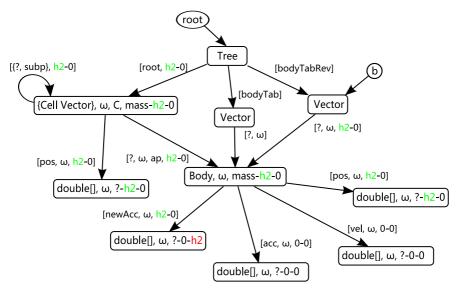

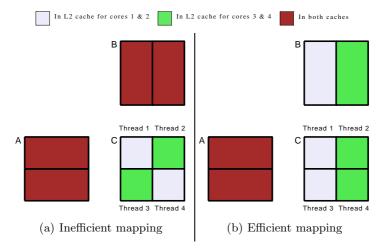

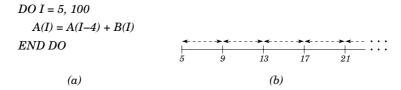

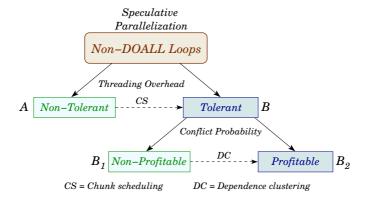

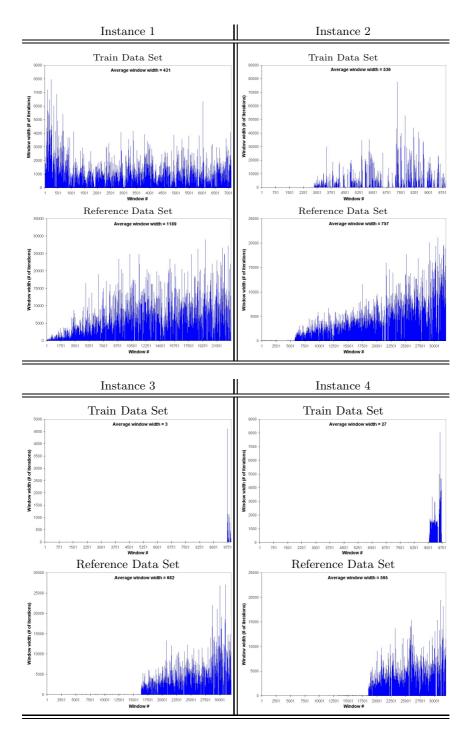

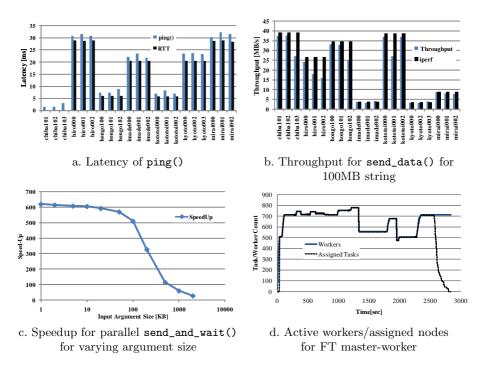

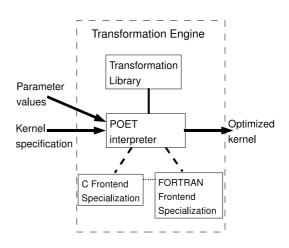

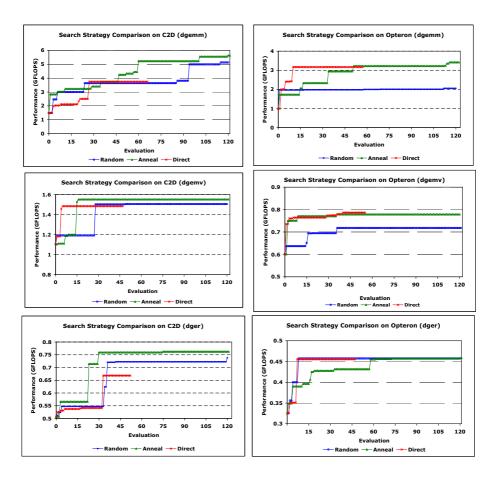

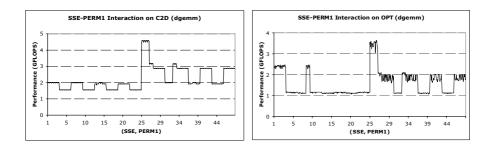

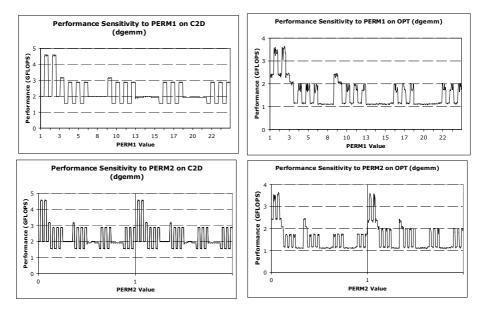

We can see that the performance scaling of this implementation is very good, with practically ideal linear scaling for a small number of processor cores. For each application, the performance of the CUDA code translated through the MCUDA framework is within 30% of the most optimized CPU implementation available. This suggests that the data tiling and locality expressed in effective CUDA kernels also gain significant performance benefits on CPUs, often replicating the results of hand-optimization for the CPU architecture. The regularly structured iterative loops of the algorithms were also preserved through the translation. The compiler vectorized the innermost loops of each application automatically, whether those were thread loops or loops already expressed in the algorithm.